Percobaan 1 - Kondisi 13:

Buatlah rangkaian seperti gambar percobaan 1 dengan menggunakan D flip flop dan output seven segment common anoda dan led dalam satu rangkaian

Rangkaian Simulasi [Kembali]

Video

[Kembali]

Prinsip Kerja [Kembali]

Power supply menuju ke seluruh switch lalu mengalirkan arus dari swtich B0 - B3 ke masing-masing kaki SET D-Flipflop. Pada switch B5 mengalirkan arus ke kaki D flipflop I. Pada switch B6 mengalirkan arus ke kaki RESET pada semua D-Flipflop. Pada switch B4 dialirkan ke salah satu kaki input gerbang AND. Pada kaki inputan gerbang AND lainnya diberikan tegangan CLOCK sehingga berubah2 inputan kakinya.

Output dari D-flipflop I dialirkan ke kaki inputan D-Flipflop II dan begitu seterusnya hingga D-Flipflop IV yang dimana setiap hasil outputnya dialirkan ke resistor 220 Ohm, LED, IC 74LS47, dan Seven Segment Common Anode.

Jika kaki inputan D pada D-FF I berlogika 1 saat kaki SET dan RESET berlogika 1, maka akan mengeluarkan output Q yaitu berlogika 1 dan diteruskan ke kaki inputan D pada D-FF II. Saat itu juga di ubah inputan D pada D-FF I berlogika 0, maka output Q D-FF I berubah menjadi 0. Namun, pada D-FF II akan meneruskan outputnya berlogika 1 ke D-FF III dan begitu seterusnya. Pada output D-FF I berlogika 0 akan diteruskan juga ke D-FF II hingga D-FF terakhir. Itulah yang disebut dengan Shift Register dimana komponen elektronika yang sekuensial untuk menyimpan dan mentransfer data secara sementara dari saluran input menuju saluran output secara digeser (shift), pergeseran data berdasarkan clock, dan Shift Register dibuat dari banyak flipflop.

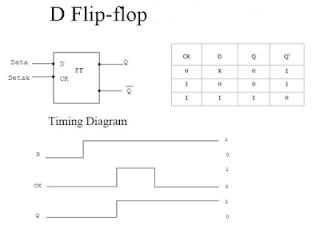

Untuk prinsip kerja dari D-FlipFlop yaitu saat kaki SET ataupun RESET berlogika 0, maka akan mengaktifkan SET-RESET sehingga input yang diberikan dari D-Flipflop tidak akan mempengaruhi output D-Fliplop. Sedangkan jika keduanya (kaki SET dan RESET) berlogika 1, maka inputan D-Fliplop akan diteruskan ke outputnya. Kaki CLK pada D-Flipflop aktif low yang berarti D-Flipflop akan bekerja jika CLK berlogika 0 maka dari itu diberikan inputan CLOCK atau berubah2 inputannya.

Hanya saja, pada CLK setiap D-Flipflop alirannya berasal dari output gerbang AND yang salah satu kakinya diberikan inputan D'CLOCK dan satu lagi terhubung dengan switch B4.

Prinsip kerja dari gerbang AND yaitu akan menghasilkan keluaran logika 1 apabila semua masukan logika 1. Sebaliknya, akan menghasilkan keluaran 0 apabila salah satu atau semua masukan berlogika 0.

Oleh karena itu, jika switch B4 berlogika 1, maka akan menghasilkan output pada gerbang AND yaitu toggle atau berubah-ubah dikarenakan adanya CLOCK. Sedangkan jika switch B4 berlogika 0, maka akan menghasilkan output pada gerbang AND yaitu akan selalu 0 yang membuat seluruh D-Flipflop tidak akan bekerja.